목차

파이프라인

파이프라인 배경(pipeline)

일반적으로 파이프라인은 한 데이터 처리 단계의 출력이 다음 단계의 입력으로 이어지는 형태의 구조를 말합니다. 이렇게 연결된 데이터 처리 단계는 한 여러 단계가 병렬적으로 수행될 수 있어 효율성의 향상을 꾀할 수 있습니다.

여기서 파이프라인도 프로세서에서 성능을 높이기 위해서 명령어 처리를 여러 단계로 나누어 단계별로 동시에 수행하여 병렬화 시키는 것을 말합니다. 프로세스 고속화, 처리량 상승효과를 얻습니다.

ARM 파이프라인

초기 ARM7TDMI까지의 ARM 코어는 3단계 파이프라인을 가졌습니다. 이후 나올 모든 여러 단계의 파이프라인도 이 3단계 파이프라인 단계를 더 나눈 형태를 보입니다.

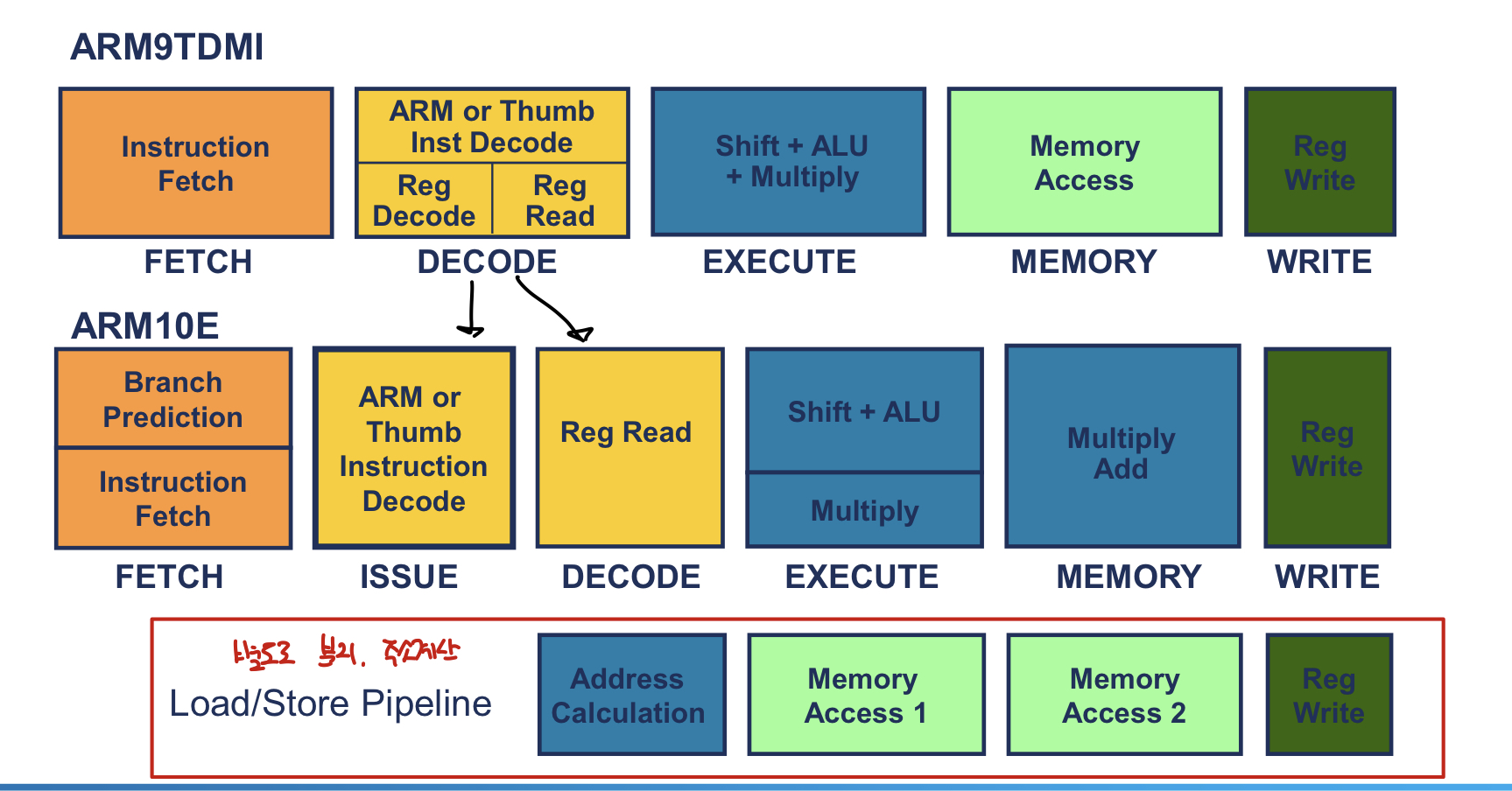

ARM9TDMI부터 여러 중요한 변경이 있엇는데 5스테이지 파이프라인으로 확장되고, Havard Memory 아키텍처를 사용하기 시작했습니다. 이 변경점으로 명령어 처리량이 획기적으로 증가했습니다.

처리량을 늘리기 위해서 파이프라인은 점점 세분화되고 길어지기 시작했는데, 이러헤 길어지면서 생기는 단점으는 분기 패널티와(분기 명령어로 인한 파이프라인 플러시) 증가와 더 복잡해진 명령어 스케줄링이 있습니다.

이를 위해 현재 코어는 분기 예측(branch prediction)을 통해 파이프라인 플러시를 피하려고 노력합니다. 정적, 동적 분기 예측과 어떤 코어는 BTAC(Branch Target Address Cache) 등을 사용한다고 합니다.

파이프라인과 레지스터

레지스터에서 Program Counter는 현재 실행 중인 명령어의 위치를 가르키는 레지스터입니다. 그리고 파이프라인에 FETCH는 명령어를 메모리에서 프로세서로 가지고 오는 단계입니다. PC는 실제로는 명령어가 실행중인 것을 가르키는게 아닌 명령어를 가져오는(fetched) 곳을 가르킵니다. 즉, PC는 파이프라인에 FETCH 단계를 가르킵니다.

Link Register는 리턴주소, 복귀 주소를 가르킵니다. 이 리턴주소는 결국 A명령어로 인해 B로 내가 이동했고, 이후 A로 복귀를 하는 것일 테니 현재 명령어 직전에 실행한 명령어가 복귀 주소일 것입니다.

파이프라인의 FETCH부분이 현재 명령어의 주소라면, DECODE 부분은 바로 직전 FETCH에 있던 명령어일 것입니다. 즉Link Register도 결국 DECODE를 가르키고 있습니다.

마지막으로 FETCH, DECODE, EXECUTE 등 파이프라인은 연속적인 과정입니다. 그렇기에 서로의 주소를 상대적으로 알 수 있습니다. 이 때 ARM명령어인지, Thumb명령어인지에 따라 간격이 조금 다르지만 위 사진과 같이 ARM의 경우 PC, PC-4, PC-8로 FECTH, DECODE, EXECUTE의 위치를 구할 수 있습니다.

파이프라인 예시

파이프라인이 모두 싱글 사이클 내에 처리되어 시간도 단계도 균일합니다.

LDR 파이프라인 예시에서는 LDR 명령어로 메모리에서 데이터를 로드하여 싱글 사이클 내에 끝나지 않을 때 fetch, decode가 stall(멈춤)되는 현상입니다.

브랜치 명령어 BL에 의한 경우도 마찬가지입니다. 브래니 명령어를 하면 그로 인해 건너 띄어지는 부분(Branch shadow) 부분이 있어 파이프라인이 깨집니다.

인터럽트가 온 경우에도 Execute를 먼저 하고 어딘가 인터럽트 핸들러로 분기할 수 있습니다.

위 경우는 모두 ARM7에서 폰 노이만 아키텍처인 경우였습니다. 이후 ARM 9에서는 하버드 아키텍처로 변경이 되며 명령어와 데이터 접근을 분리되었고 파이프라인도 5단계로 증가하며 여러 다른 것들이 추가됐습니다.

ARM10에서는 파이프라인이 6단계로 증가했으며 로드/스토어를 별도의 파이프라인으로 분리하였습니다. 또한 64비트 아키텍처가 되면서 64비트 메모리 인터페이스로 싱글 사이클에 2개의 32비트 명령어를 Fetch하는 것이 가능해졌습니다. 분기 예측 또한 정적/동적 분기 예측으로 파이프라인이 깨지는 것을 보호하기 위한 것들이 늘었습니다.

위 내용에서 생략한 많은 내용은 필요할 때 복습하는걸로...

'강의 > 컴퓨터구조' 카테고리의 다른 글

| Computer Architecture - Memory (0) | 2023.07.26 |

|---|---|

| Computer Architecture - Processor Mode (0) | 2023.06.30 |

| Computer Architecture - Registers and Instruction Set (0) | 2023.06.30 |

| Computer Architecture - Overview (0) | 2023.06.26 |