목차

Data sizes and Instruction Sets

ARM은 RISC 아키텍쳐입니다. 그래서 대부분의 명령어는 싱글 사이클에 실행됩니다.

ARM은 32bit load/store 아키텍쳐입니다. 대부분의 내부 레지스터는 32비트 폭을 가지고 있고, 허용되는 메모리 엑세스는 loads / sotres 2가지 경우입니다.

ARM에서 사용하는 경우 다음 3가지 크기로 데이터가 쓰입니다.

Halfwrod = 16 bits (2 bytes)

Word = 32 bits (4 bytes)

Double Word = 64 bits (8 bytes)

대부분 ARM 코어는 2가지 명령어 셋을 포함합니다.

1. 32-bits 크기에 Arm Instruction Set. 표준입니다.

2. Mixed 16/32 - bits Thumb Instruction Set. : Arm Instruction Set에서 많이 쓰는 명령어를 16bit로 압축해서 쓸 수 있게 만든 명령어 셋입니다.

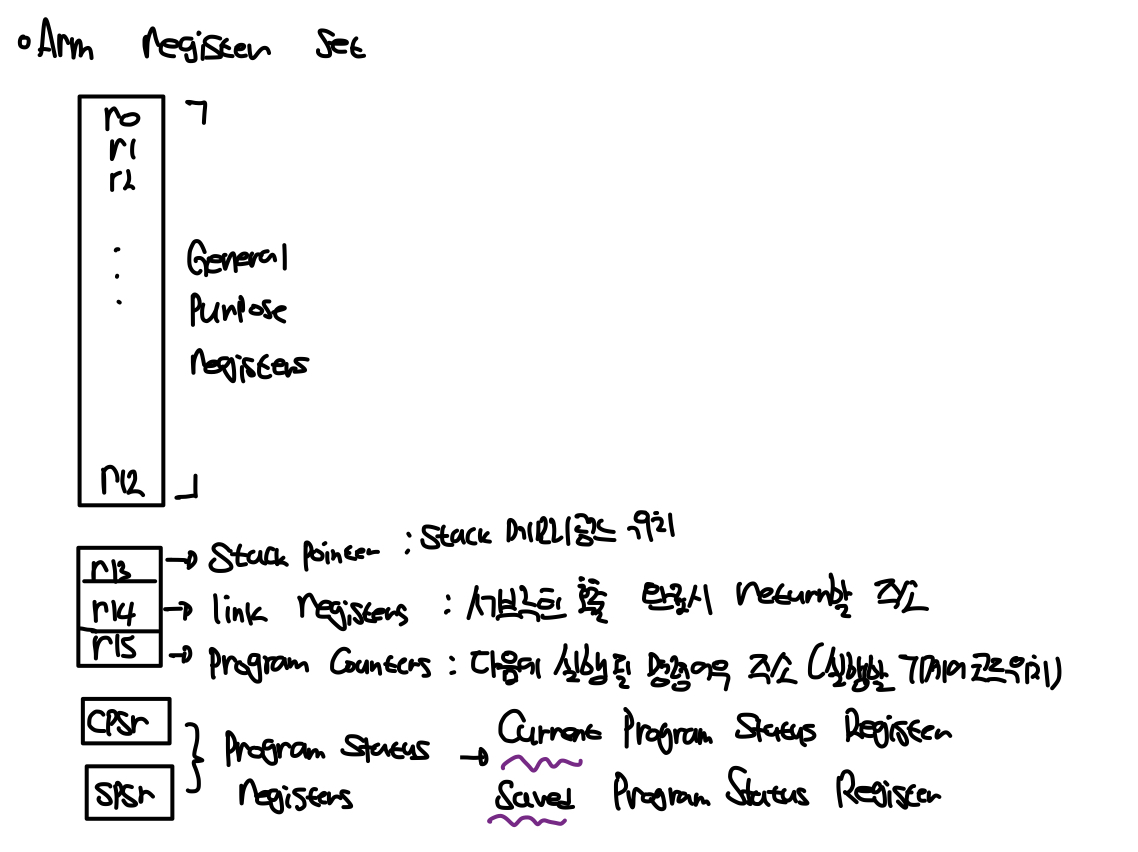

ARM Register set

AAPCS(Arm Architecture Process Call Standard)-Arm은 16개의 범용적인 레지스터를 가지고 있고 각각 목적이 있습니다.

r0 ~ r3 : 함수 파라미터가 들어갑니다. 만약에 함수의 파라미터가 4개가 넘는다면 5번째부터는 스택에 보관합니다. 함수에 리턴은 보통 r0에 보관합니다. argument, result 용도이며 스크래치 레지스터(scratch register)입니다.

*스크래치 레지스터(scratch register) : 사용자 마음대로 변경, 조작해도 되는 레지스터.

★ 재밌는 부분 : 클래스, 함수 등 모두 콤팩트할 수록 좋다고 하는데, 그 이유 중 하나로 함수의 인자가 4개가 넘는다면 이후 인자는 스택으로 가서 왔다리 갔다리 해야하기 때문에 퍼포먼스가 떨어진다고 합니다! C++ 같이 this 포인터가 있는 경우는 함수 앞에 this가 디폴트로 있기에 암 아키텍쳐에서는 3개까지가 좋다고!! 물론 상황에 맞게 해야할 것 같습니다.

r4~r11(r9제외) : 레지스터 변수 입니다.(variable register) 함수 내의 지역 변수를 담아 연산 하는데 사용합니다.

r12 : 스크래치 레지스터로 막 사용해도 됩니다. 추가로 ARM-Thumb interworking 기능에서 long branch 혹은 vaneer를 사용할 때 주소의 임시 저장소로 쓰인다고도 합니다.

r13 : 스택 포인터(Stack Pointer) : 시스템 스택에 위치를 특정하기 위한 레지스터입니다. SP가 가르키는 곳까지가 데이터가 채워진 영역이고, 그 이후부터 스택 끝까지가 비어있는 영역임을 뜻합니다.

r14 : 링크 레지스터(Link Register) : 복귀 주소를 위한 레지스터입니다. 함수 호출 등으로 서브 루틴으로 분기가 발생시, 서브 루틴이 종료되었을 때 돌아갈 리턴 주소를 저장하기 위해 사용합니다.

보통 브랜치 링크(BL) 명령으로 분기를 한 후, 서브 루틴을 수행하고 서브 루틴에 마지막에 브랜치 익스체인지(BX)명령으로 LR로 분기를 다시 하여 복귀 하는 방식을 사용합니다.

* 분기 명령어 간략소개

B : 지정 주소로 분기

BL : 분기를 하면서 LR에 주소 저장하는 명령어

BX : 지정 레지스터의 값으로 분기

r15 : 프로그램 카운터(Program Counter) : 현재 실행 중인 명령어의 위치를 가르키는 레지스터입니다.

* r14와 r15의 경우 현재 실행중인 명령어, 복귀할 명령어 주소이기 때문에 명령어의 크기로 상대적인 위치를구할 수 있습니다. 이후 파이프라인에서 소개됩니다.

PSR(Program Status Registers) : 말 그대로 현재 프로그램이 가지고 있을 상태/옵션을 저장하는 레지스터입니다.

보통 Current psr(cpsr), Saved psr(spsr) 2가지이며 오직 예외(exception) 모드에서만 있습니다. 특수한 명령어들로만 조작됩니다.

Arm instruction set

Arm 명령어 셋은 32 비트 길이에 word aligned입니다. 여기서 aligned는 각 명령어가 규격이 딱 맞는, 모두 비슷한 크기와 실행 시간을 가진다는 것을 뜻합니다.

대부분 Arm 명령어는 조건 실행이 가능하며, Load/Store 명령어는 메모리를 직접 조작하는 것은 아닙니다.

Thumb instruction set

-Thumb-

16비트 aligned로 C 코드와 찰떡으로 최적화되어 있습니다.(~65% of ARM code size)이기에 메모리 절약을 했습니다.

지엽적인, 좁은(narrow) 메모리에서 부분적으로 Arm 명령어보다 성능이 좋습니다.

Arm 명령어에 기능적으로 부분집합(subset)이며 CPSR/SPSR, coprocessors, VFP/NEON(vector floating point 연산 등)에 엑세스할 수 없고, 많은 명령이 r0~r7 레지스터 까지만 엑세스 가능합니다. 또, 조건 실행이 분기(Branch)에서만 가능합니다.

-Thumb 2-

Thumb를 확장한 것으로 16비트와 32비트 명령어 셋이 섞여있습니다. 또 CPSR/SPSR, coprocessors, VFP/NEON에 엑세스 기능을 제공하고 IT(If-Then)명령어를 통해 조건 실행을 제공합니다.

Thumb 명령어 셋에 크기 장점과 Arm 명령어 셋에 성능 장점을 섞은 형태입니다. 그렇다고 aligned가 아니냐고 하면 Thumb와 Thumb2 모두 halfword(16비트)로 algined 되어있습니다.

Floating point and NEON

-NEON-

SIMD(Single Instruction Multiple Data)란 말 그대로 하나의 명령에서 여러 데이터 조각에 대한 작업을 병렬로 수행합니다.

NEON은 SIMD를 처리해줄 수 있는 확장 도구(HW)입니다/

-VFP-

Arm 프로세서는 부동 소수점 지원하는 하드웨어 가속기가 있습니다. 보통 VFP가 없던 시기에는 애뮬레이터로 SW로 돌리기도 했다고 합니다.

-VFP and NEON-

VFP와 NEON 명령은 표준 데이터 처리 명령에 대해 별도의 레지스터 셋을 사용합니다. 레지스터 셋은 32비트(single precision), 64비트(double precision), 128비트(NEON만 사용)로 쪼개서 엑세스할 수 있습니다.

'강의 > 컴퓨터구조' 카테고리의 다른 글

| Computer Architecture - Memory (0) | 2023.07.26 |

|---|---|

| Computer Architecture - Pipeline (0) | 2023.07.25 |

| Computer Architecture - Processor Mode (0) | 2023.06.30 |

| Computer Architecture - Overview (0) | 2023.06.26 |